DIP ઉપકરણો વિશે, PCB લોકો કેટલાક ઝડપી ખાડો થૂંકતા નથી!

DIP એ પ્લગ-ઇન છે.આ રીતે પેક કરાયેલી ચિપ્સમાં પિનની બે પંક્તિઓ હોય છે, જેને ડીઆઈપી સ્ટ્રક્ચરવાળા ચિપ સોકેટમાં સીધા વેલ્ડિંગ કરી શકાય છે અથવા સમાન સંખ્યામાં છિદ્રો સાથે વેલ્ડિંગ સ્થાનો પર વેલ્ડિંગ કરી શકાય છે.પીસીબી બોર્ડ પર્ફોરેશન વેલ્ડીંગની અનુભૂતિ કરવી ખૂબ જ અનુકૂળ છે, અને મધરબોર્ડ સાથે સારી સુસંગતતા ધરાવે છે, પરંતુ તેના પેકેજિંગ વિસ્તાર અને જાડાઈ પ્રમાણમાં મોટી હોવાને કારણે, અને દાખલ કરવાની અને દૂર કરવાની પ્રક્રિયામાં પિનને નુકસાન થવું સરળ છે, નબળી વિશ્વસનીયતા.

DIP એ સૌથી લોકપ્રિય પ્લગ-ઇન પેકેજ છે, એપ્લિકેશન શ્રેણીમાં પ્રમાણભૂત લોજિક IC, મેમરી LSI, માઇક્રોકોમ્પ્યુટર સર્કિટ વગેરેનો સમાવેશ થાય છે. સ્મોલ પ્રોફાઇલ પેકેજ (SOP), SOJ (J-ટાઈપ પિન સ્મોલ પ્રોફાઇલ પેકેજ), TSOP (પાતળું નાનું) પ્રોફાઇલ પેકેજ), VSOP (ખૂબ જ નાનું પ્રોફાઇલ પેકેજ), SSOP (ઘટાડો SOP), TSSOP (પાતળો ઘટાડો SOP) અને SOT (નાનું પ્રોફાઇલ ટ્રાન્ઝિસ્ટર), SOIC (નાનું પ્રોફાઇલ ઇન્ટિગ્રેટેડ સર્કિટ), વગેરે.

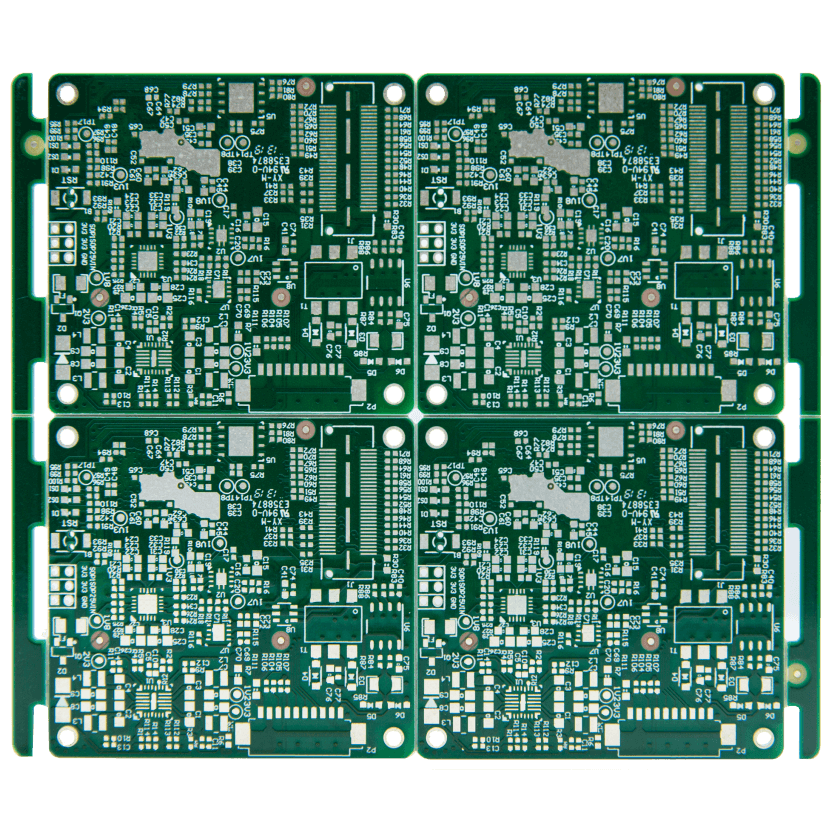

- પીસીબી પેકેજ હોલ ઉપકરણ કરતા મોટો છે

PCB પ્લગ-ઇન છિદ્રો અને પેકેજ પિન છિદ્રો સ્પષ્ટીકરણો અનુસાર દોરવામાં આવે છે.પ્લેટ બનાવતી વખતે છિદ્રોમાં કોપર પ્લેટિંગની જરૂરિયાતને કારણે, સામાન્ય સહનશીલતા વત્તા અથવા ઓછા 0.075mm છે.જો PCB પેકેજિંગ હોલ ભૌતિક ઉપકરણની પિન કરતાં ખૂબ મોટો હોય, તો તે ઉપકરણને ઢીલું કરવા, અપૂરતા ટીન, એર વેલ્ડીંગ અને અન્ય ગુણવત્તા સમસ્યાઓ તરફ દોરી જશે.

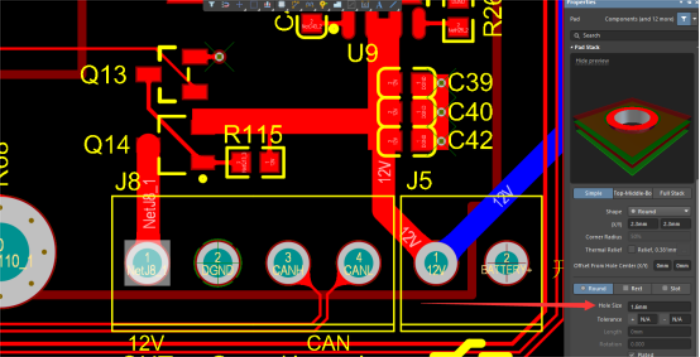

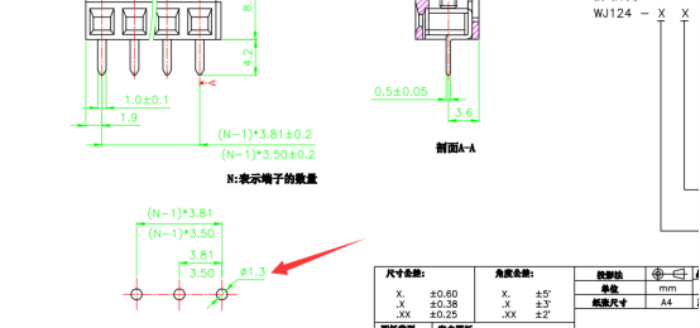

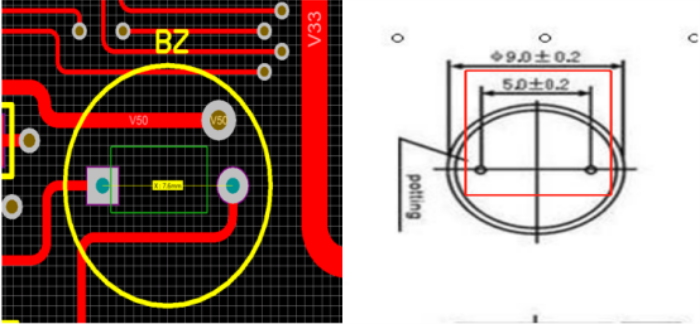

નીચેની આકૃતિ જુઓ, WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) ઉપકરણ પિનનો ઉપયોગ કરીને 1.3mm છે, PCB પેકેજિંગ હોલ 1.6mm છે, છિદ્ર વેવ વેલ્ડીંગ સ્પેસ ટાઇમ વેલ્ડીંગ માટે ખૂબ મોટી લીડ છે.

આકૃતિ સાથે જોડાયેલ, ડિઝાઇન જરૂરિયાતો અનુસાર WJ124-3.81-4P_WJ124-3.81-4P (KANGNEX) ઘટકો ખરીદો, પિન 1.3mm યોગ્ય છે.

- પીસીબી પેકેજ હોલ ઉપકરણ કરતાં નાનું છે

પ્લગ-ઇન, પરંતુ વિલ હોલ નો કોપર, જો તે સિંગલ હોય અને ડબલ પેનલ આ પદ્ધતિનો ઉપયોગ કરી શકે છે, સિંગલ અને ડબલ પેનલ બાહ્ય વિદ્યુત વહન છે, સોલ્ડર વાહક હોઈ શકે છે;મલ્ટિલેયર બોર્ડનું પ્લગ-ઇન હોલ નાનું છે, અને પીસીબી બોર્ડ ફક્ત ત્યારે જ ફરીથી બનાવી શકાય છે જો આંતરિક સ્તરમાં વિદ્યુત વહન હોય, કારણ કે આંતરિક સ્તરના વહનને રીમિંગ દ્વારા સુધારી શકાતું નથી.

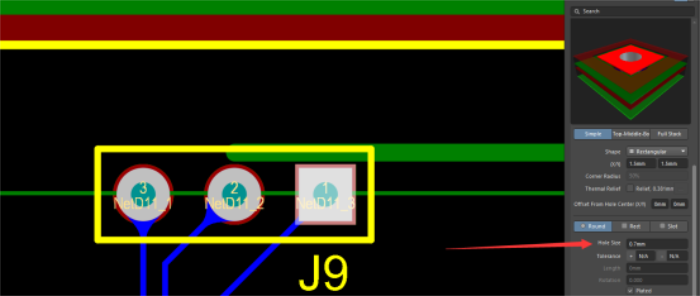

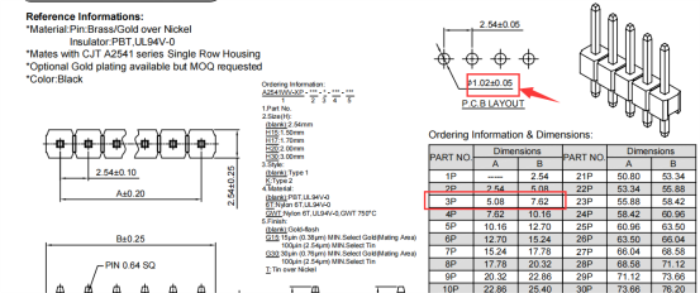

નીચેની આકૃતિમાં બતાવ્યા પ્રમાણે, A2541Hwv-3P_A2541HWV-3P (CJT) ના ઘટકો ડિઝાઇન જરૂરિયાતો અનુસાર ખરીદવામાં આવે છે.પિન 1.0mm છે, અને PCB સીલિંગ પેડ હોલ 0.7mm છે, પરિણામે દાખલ કરવામાં નિષ્ફળતા મળે છે.

A2541Hwv-3P_A2541HWV-3P (CJT) ના ઘટકો ડિઝાઇન જરૂરિયાતો અનુસાર ખરીદવામાં આવે છે.પિન 1.0mm સાચો છે.

- પેકેજ પિન અંતર ઉપકરણ અંતરથી અલગ છે

ડીઆઈપી ઉપકરણના પીસીબી સીલિંગ પેડમાં માત્ર પિન જેટલું જ બાકોરું નથી, પરંતુ પિન છિદ્રો વચ્ચે સમાન અંતરની પણ જરૂર છે.જો પિન છિદ્રો અને ઉપકરણ વચ્ચેનું અંતર અસંગત હોય, તો એડજસ્ટેબલ ફૂટ સ્પેસિંગવાળા ભાગો સિવાય, ઉપકરણ દાખલ કરી શકાતું નથી.

નીચેની આકૃતિમાં બતાવ્યા પ્રમાણે, PCB પેકેજિંગનું પિન હોલ અંતર 7.6mm છે, અને ખરીદેલા ઘટકોના પિન હોલનું અંતર 5.0mm છે.2.6mm નો તફાવત ઉપકરણને બિનઉપયોગી તરફ દોરી જાય છે.

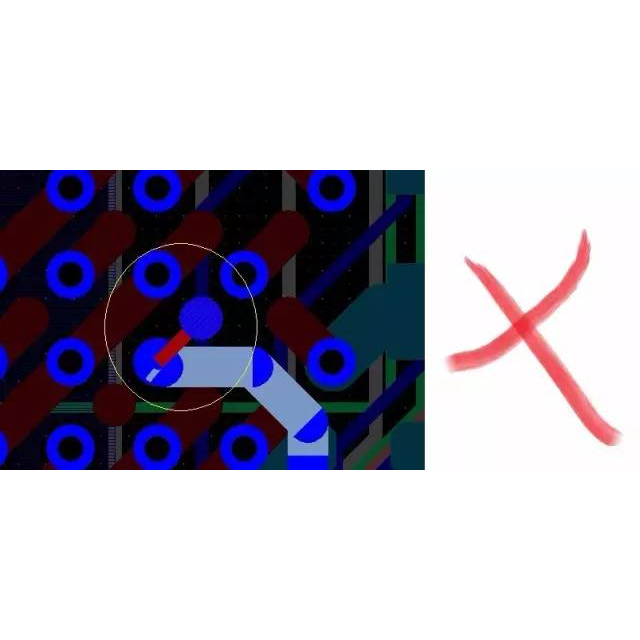

- PCB પેકેજિંગ છિદ્રો ખૂબ નજીક છે

PCB ડિઝાઇન, ડ્રોઇંગ અને પેકેજિંગમાં, પિન છિદ્રો વચ્ચેના અંતર પર ધ્યાન આપવું જરૂરી છે.જો એકદમ પ્લેટ જનરેટ કરી શકાતી હોય તો પણ, પિન છિદ્રો વચ્ચેનું અંતર નાનું હોય છે, વેવ સોલ્ડરિંગ દ્વારા એસેમ્બલી દરમિયાન ટીન શોર્ટ સર્કિટનું કારણ બને છે.

નીચેની આકૃતિમાં બતાવ્યા પ્રમાણે, નાના પિન અંતરને કારણે શોર્ટ સર્કિટ થઈ શકે છે.સોલ્ડરિંગ ટીનમાં શોર્ટ સર્કિટ થવાના ઘણા કારણો છે.જો ડિઝાઇનના અંતે એસેમ્બલીબિલીટીને અગાઉથી અટકાવી શકાય, તો સમસ્યાઓની ઘટનાઓ ઘટાડી શકાય છે.

- સમસ્યા નું વર્ણન

ઉત્પાદન ડીઆઈપીના વેવ ક્રેસ્ટ વેલ્ડીંગ પછી, એવું જાણવા મળ્યું કે નેટવર્ક સોકેટના નિશ્ચિત પગની સોલ્ડર પ્લેટ પર ટીનની ગંભીર અછત હતી, જે એર વેલ્ડીંગની હતી.

- સમસ્યાની અસર

પરિણામે, નેટવર્ક સોકેટ અને પીસીબી બોર્ડની સ્થિરતા વધુ ખરાબ થાય છે, અને ઉત્પાદનના ઉપયોગ દરમિયાન સિગ્નલ પિન ફૂટનું બળ લાગુ કરવામાં આવશે, જે આખરે સિગ્નલ પિન ફૂટના જોડાણ તરફ દોરી જશે, જે ઉત્પાદનને અસર કરશે. પ્રદર્શન અને વપરાશકર્તાઓના ઉપયોગમાં નિષ્ફળતાના જોખમનું કારણ બને છે.

- સમસ્યા વિસ્તરણ

નેટવર્ક સોકેટની સ્થિરતા નબળી છે, સિગ્નલ પિનની કનેક્શન કામગીરી નબળી છે, ગુણવત્તા સમસ્યાઓ છે, તેથી તે વપરાશકર્તા માટે સુરક્ષા જોખમો લાવી શકે છે, અંતિમ નુકસાન અકલ્પનીય છે.

- DIP ઉપકરણ પિન સંબંધિત ઘણી સમસ્યાઓ છે, અને ઘણા મુખ્ય મુદ્દાઓને અવગણવામાં સરળ છે, પરિણામે અંતિમ સ્ક્રેપ બોર્ડ.તો એકવાર અને બધા માટે આવી સમસ્યાઓને ઝડપથી અને સંપૂર્ણપણે કેવી રીતે હલ કરવી?

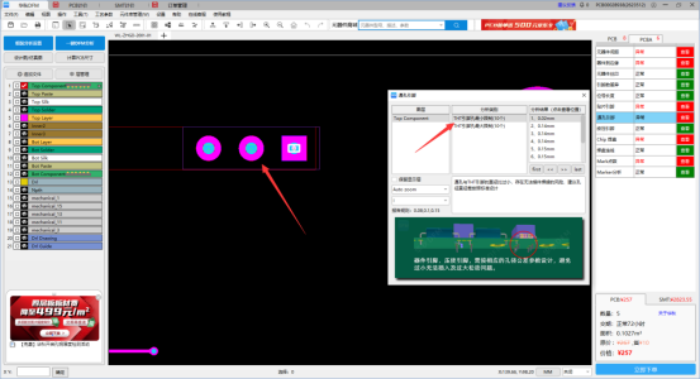

- અહીં, અમારા CHIPSTOCK.TOP સોફ્ટવેરના એસેમ્બલી અને વિશ્લેષણ કાર્યનો ઉપયોગ DIP ઉપકરણોની પિન પર વિશેષ નિરીક્ષણ કરવા માટે થઈ શકે છે.નિરીક્ષણ વસ્તુઓમાં છિદ્રો દ્વારા પિનની સંખ્યા, THT પિનની મોટી મર્યાદા, THT પિનની નાની મર્યાદા અને THT પિનની વિશેષતાઓનો સમાવેશ થાય છે.પિનની નિરીક્ષણ વસ્તુઓ મૂળભૂત રીતે DIP ઉપકરણોની ડિઝાઇનમાં સંભવિત સમસ્યાઓને આવરી લે છે.

- PCB ડિઝાઇન પૂર્ણ થયા પછી, PCBA એસેમ્બલી વિશ્લેષણ કાર્યનો ઉપયોગ અગાઉથી ડિઝાઇન ખામીઓ શોધવા, ઉત્પાદન પહેલાં ડિઝાઇનની વિસંગતતાઓને ઉકેલવા અને એસેમ્બલી પ્રક્રિયામાં ડિઝાઇન સમસ્યાઓ ટાળવા, ઉત્પાદનમાં વિલંબ અને સંશોધન અને વિકાસ ખર્ચને વેડફવા માટે વાપરી શકાય છે.

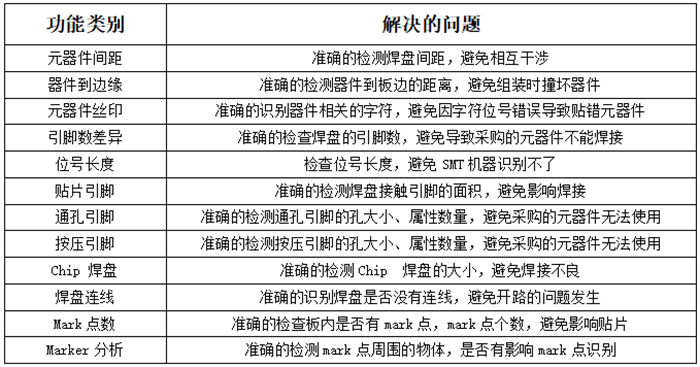

- તેના એસેમ્બલી વિશ્લેષણ કાર્યમાં 10 મુખ્ય વસ્તુઓ અને 234 દંડ વસ્તુઓ નિરીક્ષણ નિયમો છે, જે તમામ સંભવિત એસેમ્બલી સમસ્યાઓને આવરી લે છે, જેમ કે ઉપકરણ વિશ્લેષણ, પિન વિશ્લેષણ, પેડ વિશ્લેષણ, વગેરે, જે વિવિધ પ્રકારની ઉત્પાદન પરિસ્થિતિઓને હલ કરી શકે છે જેની ઇજનેરો અગાઉથી અપેક્ષા રાખી શકતા નથી.