કેપેસિટર એ સર્કિટ ડિઝાઇનમાં સૌથી વધુ ઉપયોગમાં લેવાતું ઉપકરણ છે, તે નિષ્ક્રિય ઘટકોમાંનું એક છે, સક્રિય ઉપકરણ એ ફક્ત સક્રિય ઉપકરણ તરીકે ઓળખાતા ઉપકરણના ઊર્જા (ઇલેક્ટ્રિકલ) સ્ત્રોતની જરૂરિયાત છે, ઉપકરણનો ઊર્જા (ઇલેક્ટ્રિકલ) સ્ત્રોત વિના નિષ્ક્રિય ઉપકરણ છે. .

કેપેસિટરની ભૂમિકા અને ઉપયોગ સામાન્ય રીતે ઘણા પ્રકારના હોય છે, જેમ કે: બાયપાસની ભૂમિકા, ડીકોપલિંગ, ફિલ્ટરિંગ, ઊર્જા સંગ્રહ; ઓસિલેશન, સિંક્રનાઇઝેશન અને સમય સ્થિરતાની ભૂમિકાની પૂર્ણતામાં.

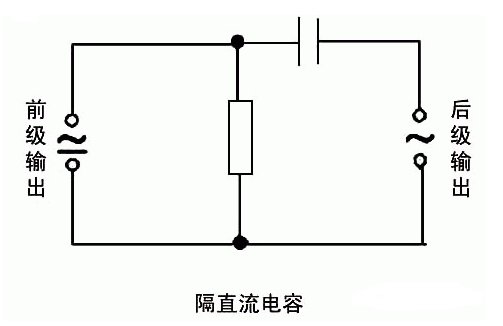

ડીસી આઇસોલેશન: કાર્ય એ ડીસીને અટકાવવાનું અને ACને પસાર થવા દેવાનું છે.

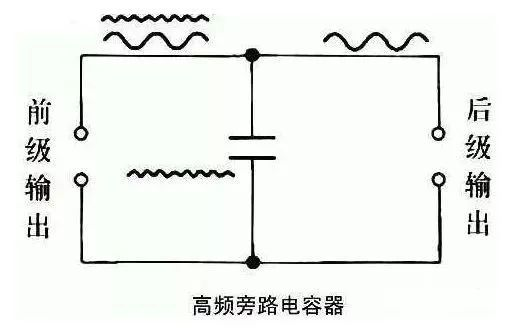

બાયપાસ (ડીકપલિંગ) : એસી સર્કિટમાં અમુક સમાંતર ઘટકો માટે નીચા-અવરોધનો માર્ગ પૂરો પાડે છે.

બાયપાસ કેપેસિટર: બાયપાસ કેપેસિટર, જેને ડીકોપલિંગ કેપેસિટર તરીકે પણ ઓળખવામાં આવે છે, તે ઊર્જા સંગ્રહ ઉપકરણ છે જે ઉપકરણને ઊર્જા પ્રદાન કરે છે. તે કેપેસિટરની આવર્તન અવબાધ લાક્ષણિકતાઓનો ઉપયોગ કરે છે, આદર્શ કેપેસિટરની આવર્તન લાક્ષણિકતાઓનો ઉપયોગ કરે છે જેમ જેમ આવર્તન વધે છે, અવબાધ ઘટે છે, તળાવની જેમ, તે આઉટપુટ વોલ્ટેજ આઉટપુટને એકસમાન બનાવી શકે છે, લોડ વોલ્ટેજની વધઘટ ઘટાડી શકે છે. બાયપાસ કેપેસિટર પાવર સપ્લાય પિન અને લોડ ડિવાઇસના ગ્રાઉન્ડ પિનની શક્ય તેટલું નજીક હોવું જોઈએ, જે અવબાધની આવશ્યકતા છે.

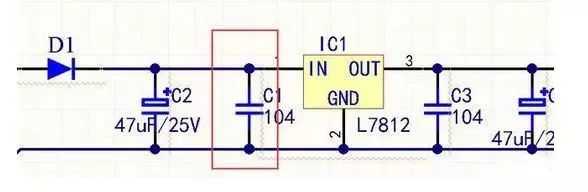

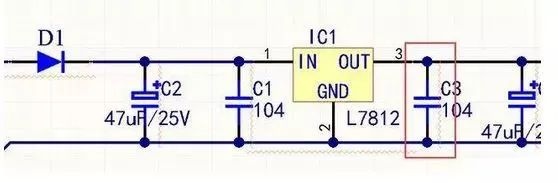

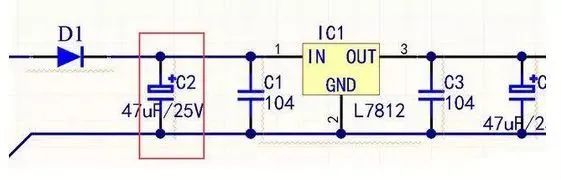

PCB દોરતી વખતે, એ હકીકત પર વિશેષ ધ્યાન આપો કે જ્યારે તે ઘટકની નજીક હોય ત્યારે જ તે જમીનની સંભવિત ઊંચાઈ અને વધુ પડતા વોલ્ટેજ અથવા અન્ય સિગ્નલ ટ્રાન્સમિશનને કારણે થતા અવાજને દબાવી શકે છે. તેને સ્પષ્ટ રીતે કહીએ તો, DC પાવર સપ્લાયના AC ઘટકને કેપેસિટર દ્વારા પાવર સપ્લાય સાથે જોડવામાં આવે છે, જે DC પાવર સપ્લાયને શુદ્ધ કરવાની ભૂમિકા ભજવે છે. નીચેની આકૃતિમાં C1 એ બાયપાસ કેપેસિટર છે, અને ડ્રોઇંગ IC1 ની શક્ય તેટલી નજીક હોવી જોઈએ.

ડીકોપ્લીંગ કેપેસીટર: ડીકોપ્લીંગ કેપેસીટર એ ફિલ્ટર ઓબ્જેક્ટ તરીકે આઉટપુટ સિગ્નલની દખલગીરી છે, ડીકોપ્લીંગ કેપેસીટર બેટરીની સમકક્ષ છે, તેના ચાર્જ અને ડિસ્ચાર્જનો ઉપયોગ, જેથી એમ્પ્લીફાઈડ સિગ્નલ વર્તમાનના પરિવર્તનથી ખલેલ પહોંચે નહીં. . તેની ક્ષમતા સિગ્નલની આવર્તન અને લહેરિયાંને દબાવવાની ડિગ્રી પર આધારિત છે, અને ડીકોપ્લિંગ કેપેસિટર ડ્રાઇવ સર્કિટ વર્તમાનમાં ફેરફારોને પહોંચી વળવા અને એકબીજા વચ્ચેના જોડાણની દખલને ટાળવા માટે "બેટરી" ભૂમિકા ભજવે છે.

બાયપાસ કેપેસિટર વાસ્તવમાં ડી-કપ્લ્ડ છે, પરંતુ બાયપાસ કેપેસિટર સામાન્ય રીતે ઉચ્ચ-આવર્તન બાયપાસનો સંદર્ભ આપે છે, એટલે કે, ઓછા-અવરોધ મુક્ત માર્ગના ઉચ્ચ-આવર્તન સ્વિચિંગ અવાજને સુધારવા માટે. ઉચ્ચ-આવર્તન બાયપાસ કેપેસીટન્સ સામાન્ય રીતે નાનું હોય છે, અને રેઝોનન્ટ આવર્તન સામાન્ય રીતે 0.1F, 0.01F, વગેરે હોય છે. ડીકોપલિંગ કેપેસિટરની ક્ષમતા સામાન્ય રીતે મોટી હોય છે, જે સર્કિટમાં વિતરિત પરિમાણોના આધારે 10F અથવા વધુ હોઈ શકે છે. ડ્રાઇવ વર્તમાનમાં ફેરફાર.

તેમની વચ્ચેનો તફાવત: બાયપાસ એ ઑબ્જેક્ટ તરીકે ઇનપુટ સિગ્નલમાં દખલગીરીને ફિલ્ટર કરવાનો છે, અને ડિકપલિંગ એ ઑબ્જેક્ટ તરીકે આઉટપુટ સિગ્નલમાં હસ્તક્ષેપને ફિલ્ટર કરવાનો છે જેથી દખલગીરીના સંકેતને પાવર સપ્લાય પર પાછા ફરતા અટકાવવામાં આવે.

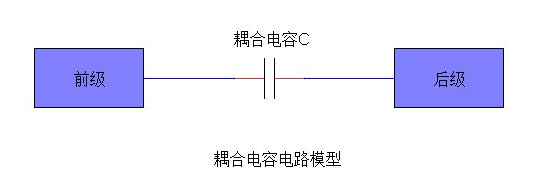

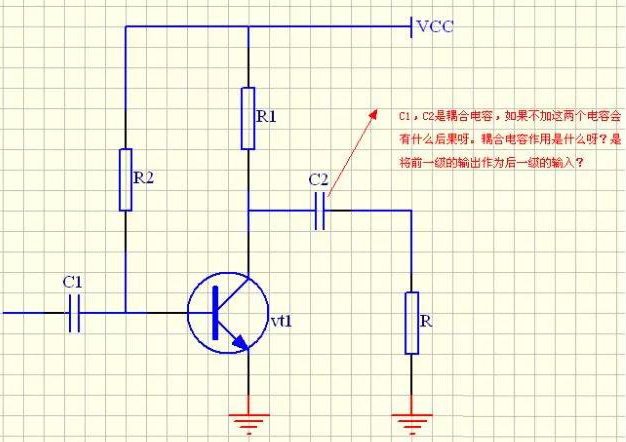

કપલિંગ: બે સર્કિટ વચ્ચેના જોડાણ તરીકે કામ કરે છે, જે એસી સિગ્નલોને પસાર થવા દે છે અને આગલા સ્તરના સર્કિટમાં ટ્રાન્સમિટ કરે છે.

કેપેસિટરનો ઉપયોગ કપ્લીંગ ઘટક તરીકે પૂર્વ સિગ્નલને પાછલા તબક્કામાં ટ્રાન્સમિટ કરવા માટે અને પછીના સ્ટેજ પર અગાઉના ડાયરેક્ટ કરંટના પ્રભાવને અવરોધિત કરવા માટે થાય છે, જેથી સર્કિટ ડીબગીંગ સરળ હોય અને કામગીરી સ્થિર રહે. જો એસી સિગ્નલ એમ્પ્લીફિકેશન કેપેસિટર વિના બદલાતું નથી, પરંતુ તમામ સ્તરે કાર્યકારી બિંદુને ફરીથી ડિઝાઇન કરવાની જરૂર છે, આગળ અને પાછળના તબક્કાના પ્રભાવને લીધે, કાર્યકારી બિંદુને ડીબગ કરવું ખૂબ મુશ્કેલ છે, અને તે પ્રાપ્ત કરવું લગભગ અશક્ય છે. બહુવિધ સ્તરો.

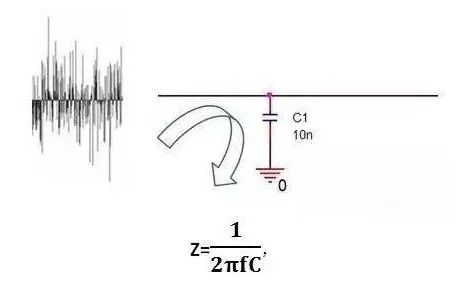

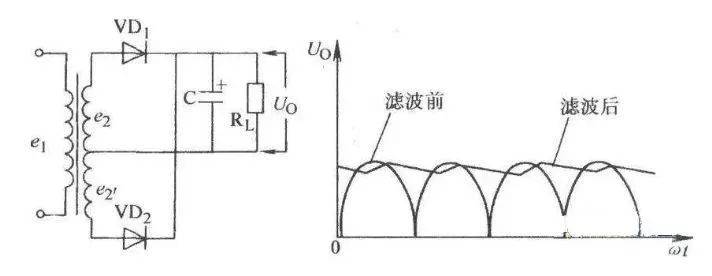

ફિલ્ટર: આ સર્કિટ માટે ખૂબ જ મહત્વપૂર્ણ છે, CPU પાછળ કેપેસિટર મૂળભૂત રીતે આ ભૂમિકા છે.

એટલે કે, ફ્રિક્વન્સી f જેટલી વધુ, કેપેસિટરની અવબાધ Z જેટલી નાની. જ્યારે ઓછી આવર્તન, કેપેસીટન્સ C કારણ કે અવબાધ Z પ્રમાણમાં મોટો હોય છે, ત્યારે ઉપયોગી સંકેતો સરળતાથી પસાર થઈ શકે છે; ઉચ્ચ આવર્તન પર, કેપેસિટર C પહેલેથી જ અવબાધ Z ને કારણે ખૂબ નાનું છે, જે GND માટે ટૂંકા-સર્કિટિંગ ઉચ્ચ-આવર્તન અવાજની સમકક્ષ છે.

ફિલ્ટર ક્રિયા: આદર્શ વીજધારિતા, ક્ષમતા જેટલી મોટી, અવબાધ જેટલો નાનો, પસાર થવાની આવર્તન વધુ. ઇલેક્ટ્રોલિટીક કેપેસિટર્સ સામાન્ય રીતે 1uF કરતા વધુ હોય છે, જેમાં મોટા ઇન્ડક્ટન્સ ઘટક હોય છે, તેથી ઉચ્ચ આવર્તન પછી અવબાધ મોટો હશે. આપણે ઘણીવાર જોઈએ છીએ કે કેટલીકવાર નાના કેપેસિટરની સમાંતર મોટા કેપેસીટન્સ ઈલેક્ટ્રોલાઈટીક કેપેસીટર હોય છે, હકીકતમાં, ઓછી આવર્તન દ્વારા મોટા કેપેસીટર, ઉચ્ચ આવર્તન દ્વારા નાની કેપેસીટન્સ, જેથી ઉચ્ચ અને નીચી ફ્રીક્વન્સીને સંપૂર્ણપણે ફિલ્ટર કરી શકાય. કેપેસિટરની આવર્તન જેટલી વધારે છે, એટેન્યુએશન વધારે છે, કેપેસિટર એક તળાવ જેવું છે, પાણીના થોડા ટીપા તેમાં મોટો ફેરફાર કરવા માટે પૂરતા નથી, એટલે કે, વોલ્ટેજની વધઘટ એ મહાન સમય નથી જ્યારે વોલ્ટેજ બફર કરી શકાય છે.

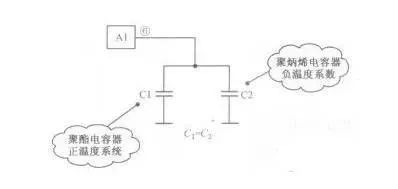

આકૃતિ C2 તાપમાન વળતર: અન્ય ઘટકોની અપૂરતી તાપમાન અનુકૂલનક્ષમતાની અસરને વળતર આપીને સર્કિટની સ્થિરતામાં સુધારો કરવો.

વિશ્લેષણ: કારણ કે ટાઇમિંગ કેપેસિટરની ક્ષમતા લાઇન ઓસિલેટરની ઓસિલેશન ફ્રીક્વન્સી નક્કી કરે છે, ટાઇમિંગ કેપેસિટરની ક્ષમતા ખૂબ જ સ્થિર હોવી જરૂરી છે અને પર્યાવરણીય ભેજના ફેરફાર સાથે બદલાતી નથી, જેથી ઓસિલેશન આવર્તન નક્કી કરી શકાય. રેખા ઓસિલેટર સ્થિર. તેથી, સકારાત્મક અને નકારાત્મક તાપમાન ગુણાંકવાળા કેપેસિટર્સનો ઉપયોગ તાપમાન પૂરક કરવા માટે સમાંતરમાં થાય છે. જ્યારે ઓપરેટિંગ તાપમાન વધે છે, ત્યારે C1 ની ક્ષમતા વધી રહી છે, જ્યારે C2 ની ક્ષમતા ઘટી રહી છે. સમાંતર બે કેપેસિટરની કુલ ક્ષમતા એ બે કેપેસિટરની ક્ષમતાઓનો સરવાળો છે. એક ક્ષમતા વધી રહી છે જ્યારે બીજી ઘટી રહી છે, કુલ ક્ષમતા મૂળભૂત રીતે અપરિવર્તિત છે. તેવી જ રીતે, જ્યારે તાપમાનમાં ઘટાડો થાય છે, ત્યારે એક કેપેસિટરની ક્ષમતામાં ઘટાડો થાય છે અને બીજામાં વધારો થાય છે, અને કુલ ક્ષમતા મૂળભૂત રીતે અપરિવર્તિત હોય છે, જે ઓસિલેશન ફ્રીક્વન્સીને સ્થિર કરે છે અને તાપમાન વળતરનો હેતુ પ્રાપ્ત કરે છે.

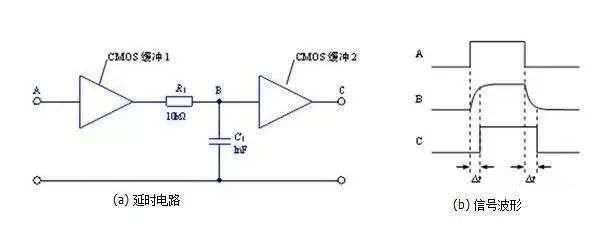

સમય: સર્કિટના સમયની સ્થિરતા નક્કી કરવા માટે કેપેસિટરનો ઉપયોગ રેઝિસ્ટર સાથે કરવામાં આવે છે.

જ્યારે ઇનપુટ સિગ્નલ નીચાથી ઊંચા તરફ જાય છે, ત્યારે RC સર્કિટ બફરિંગ પછી ઇનપુટ થાય છે 1. કેપેસિટર ચાર્જિંગની લાક્ષણિકતા બિંદુ B પરના સિગ્નલને ઇનપુટ સિગ્નલ સાથે તરત જ કૂદકો મારતો નથી, પરંતુ ધીમે ધીમે વધવાની પ્રક્રિયા ધરાવે છે. જ્યારે પૂરતું મોટું થાય છે, ત્યારે બફર 2 પલટી જાય છે, પરિણામે આઉટપુટ પર નીચાથી ઊંચા સુધી વિલંબિત કૂદકો આવે છે.

સમયની સ્થિરતા: ઉદાહરણ તરીકે સામાન્ય RC શ્રેણીના સંકલિત સર્કિટને લેતા, જ્યારે ઇનપુટ સિગ્નલ વોલ્ટેજ ઇનપુટ એન્ડ પર લાગુ થાય છે, ત્યારે કેપેસિટર પરનો વોલ્ટેજ ધીમે ધીમે વધે છે. વોલ્ટેજ વધવાની સાથે ચાર્જિંગ કરંટ ઘટે છે, રેઝિસ્ટર R અને કેપેસિટર C શ્રેણીમાં ઇનપુટ સિગ્નલ VI સાથે જોડાયેલા હોય છે, અને કેપેસિટર C માંથી આઉટપુટ સિગ્નલ V0, જ્યારે RC (τ) મૂલ્ય અને ઇનપુટ ચોરસ તરંગ પહોળાઈ tW મીટ: τ “tW”, આ સર્કિટને એકીકૃત સર્કિટ કહેવામાં આવે છે.

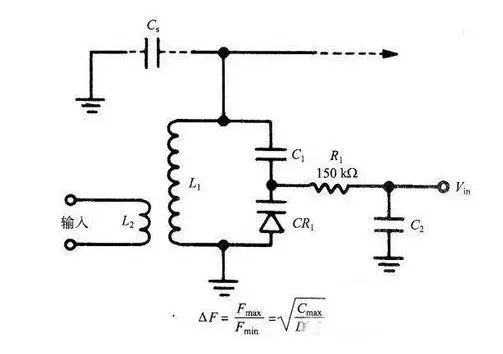

ટ્યુનિંગ: આવર્તન આધારિત સર્કિટનું વ્યવસ્થિત ટ્યુનિંગ, જેમ કે સેલ ફોન, રેડિયો અને ટેલિવિઝન સેટ.

કારણ કે IC ટ્યુન કરેલ ઓસીલેટીંગ સર્કિટની રેઝોનન્ટ આવર્તન એ IC નું કાર્ય છે, અમે શોધીએ છીએ કે ઓસીલેટીંગ સર્કિટની મહત્તમ અને લઘુત્તમ રેઝોનન્ટ આવર્તનનો ગુણોત્તર કેપેસીટન્સ રેશિયોના વર્ગમૂળ સાથે બદલાય છે. કેપેસીટન્સ રેશિયો અહીં કેપેસીટન્સના ગુણોત્તરનો ઉલ્લેખ કરે છે જ્યારે રિવર્સ બાયસ વોલ્ટેજ કેપેસીટન્સથી સૌથી ઓછું હોય છે જ્યારે રિવર્સ બાયસ વોલ્ટેજ સૌથી વધુ હોય છે. તેથી, સર્કિટની ટ્યુનિંગ લાક્ષણિકતા વળાંક (બાયસ-રેઝોનન્ટ આવર્તન) મૂળભૂત રીતે પેરાબોલા છે.

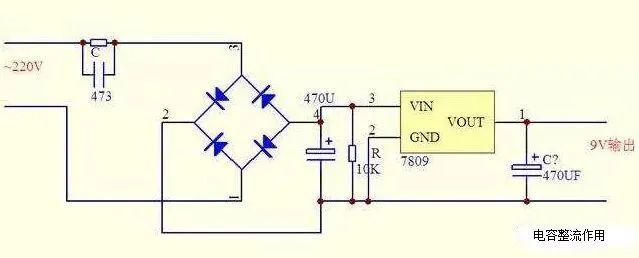

રેક્ટિફાયર: પૂર્વનિર્ધારિત સમયે અર્ધ-બંધ કંડક્ટર સ્વિચ ઘટકને ચાલુ અથવા બંધ કરવું.

ઊર્જા સંગ્રહ: જ્યારે જરૂરી હોય ત્યારે પ્રકાશન માટે વિદ્યુત ઊર્જાનો સંગ્રહ કરવો. જેમ કે કેમેરા ફ્લેશ, હીટિંગ સાધનો વગેરે.

સામાન્ય રીતે, ઇલેક્ટ્રોલિટીક કેપેસિટર્સ પાસે ઊર્જા સંગ્રહની ભૂમિકા હશે, ખાસ ઊર્જા સંગ્રહ કેપેસિટર્સ માટે, કેપેસિટીવ ઊર્જા સંગ્રહની પદ્ધતિ ડબલ ઇલેક્ટ્રિક લેયર કેપેસિટર્સ અને ફેરાડે કેપેસિટર્સ છે. તેનું મુખ્ય સ્વરૂપ સુપરકેપેસિટર એનર્જી સ્ટોરેજ છે, જેમાં સુપરકેપેસિટર્સ ડબલ ઇલેક્ટ્રિક લેયર્સના સિદ્ધાંતનો ઉપયોગ કરીને કેપેસિટર છે.

જ્યારે સુપરકેપેસિટરની બે પ્લેટ પર લાગુ વોલ્ટેજ લાગુ કરવામાં આવે છે, ત્યારે પ્લેટનો પોઝિટિવ ઇલેક્ટ્રોડ હકારાત્મક ચાર્જ સંગ્રહિત કરે છે, અને નકારાત્મક પ્લેટ નકારાત્મક ચાર્જને સંગ્રહિત કરે છે, જેમ કે સામાન્ય કેપેસિટરમાં. સુપરકેપેસિટરની બે પ્લેટો પરના ચાર્જ દ્વારા ઉત્પન્ન થયેલ ઇલેક્ટ્રિક ફિલ્ડ હેઠળ, ઇલેક્ટ્રોલાઇટના આંતરિક ઇલેક્ટ્રિક ક્ષેત્રને સંતુલિત કરવા માટે ઇલેક્ટ્રોલાઇટ અને ઇલેક્ટ્રોડ વચ્ચેના ઇન્ટરફેસ પર વિપરીત ચાર્જ રચાય છે.

આ સકારાત્મક ચાર્જ અને નકારાત્મક ચાર્જ બે અલગ-અલગ તબક્કાઓ વચ્ચે સંપર્ક સપાટી પર પોઝિટિવ અને નેગેટિવ ચાર્જ વચ્ચે ખૂબ જ ટૂંકા અંતર સાથે વિરુદ્ધ સ્થિતિમાં ગોઠવાયેલા છે, અને આ ચાર્જ વિતરણ સ્તરને ડબલ ઇલેક્ટ્રિક સ્તર કહેવામાં આવે છે, તેથી ઇલેક્ટ્રિક ક્ષમતા ખૂબ મોટી છે.

પોસ્ટ સમય: ઓગસ્ટ-15-2023